Проектирование на основе стандартных ячеек

Стиль этой статьи неэнциклопедичен или нарушает нормы литературного русского языка. |

Проектирование на основе стандартных ячеек (англ. standard cell) — метод проектирования интегральных схем с преобладанием цифровых элементов. В данном методе наиболее низкий уровень проектирования СБИС скрыт от проектировщика абстрактными логическими элементами (например, узел NAND). Методология проектирования на базе ячеек позволяет одним разработчикам сфокусироваться на высокоуровневом аспекте цифрового дизайна, пока другие разработчики заняты физическими реализациями ячеек. Вместе с достижениями полупроводникового производства методология стандартных ячеек отвечает за возможность проектирования как простых интегральных схем, число которых составляет несколько тысяч транзисторов, так и сложнейших: СБИС и систем на кристалле (СнК) с числом транзисторов, достигающим десятков миллиардов[1][2].

Конструкция стандартной ячейки

правитьСтандартная ячейка состоит из группы транзисторов и соединений между ними, которые реализуют либо некоторую логическую функцию (AND, OR, XOR, XNOR, инвертор), либо элемент хранения (например, триггеры flipflop или latch). Простейшие ячейки являются прямым представлением элементарных булевых функций NAND, NOR, XOR; часто используются более сложные ячейки (полный двухбитовый сумматор или мультиплексированный D-триггер). Логическая функциональность ячейки называется её logical view: поведение ячейки соответствует таблице истинности для комбинационной логики и таблице изменения состояний (en:state transition table) (для последовательной логики см. секвенциальная логика).

Обычно изначально стандартная ячейка проектируется на уровне транзисторов, в форме транзисторного en:netlist. Он представляет собой описание каждого транзистора и соединений между ними; также нетлист включает в себя порты — точки подключения к другим частям микропроцессора. Разработчики ячеек используют CAD-системы, например, SPICE для симуляции электрического поведения нетлиста, подавая ему на вход различные сигналы и получая вычисленный аналоговый ответ схемы вместе с его временными характеристиками. Симуляцией проверяется, что данный нетлист действительно выполняет требуемую функцию, и предсказывается потребляемая мощность и задержка распространения сигналов.

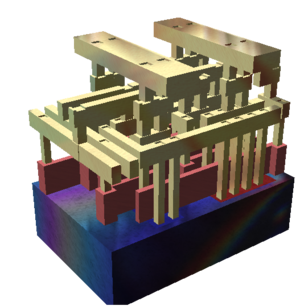

Поскольку логическое и нетлист-представления шаблоны полезны лишь при абстрактном проектировании и симуляции, а не при производстве микросхемы, для стандартной ячейки требуется разработка физической реализации. Она называется layout view и является наинизшим уровнем абстракции при разработке. С точки зрения производителя данное представление ячеек является наиболее важным, так как из него просто получить маски для литографии. Представление ячейки разделено на базовые слои, которые соответствуют различным структурам транзистора и межсоединений, замыкающих между собой выводы транзисторов.

Для типичной булевой функции можно разработать множество транзисторных нетлистов, которые будут функционально эквивалентны. Также, для типичного нетлиста можно разработать множество вариантов реализации в виде layout view, удовлетворяющих требованиям к производительности нетлиста. Задачей разработчика является уменьшение стоимости производства интегральной схемы (обычно через минимизацию занимаемой площади) при сохранении скорости ячейки и требований по мощности.

Библиотеки стандартных ячеек

правитьБиблиотека стандартных ячеек — это коллекция низкоуровневых ячеек для логических функций, триггеров, регистров и буферов. Все ячейки реализованы с фиксированной высотой и переменной шириной. Ключевым свойством библиотек является одинаковость высот ячеек, что позволяет располагать их рядами, упрощая задачу автоматического расположения элементов. Ячейки обычно оптимизированы для уменьшения занимаемой площади и задержки.

Типичная библиотека условно делится на две части:

- Front-end включает в себя логические описания (Verilog, VHDL), характеризацию ячеек (Synopsys Liberty, ALF и SDF), а также вспомогательные элементы для функциональной верификации (MET, Fastscan и т. д).

- Back-end содержит описания, относящиеся к физической реализации ячеек. Это физические абстракции в формате Cadence LEF format либо Synopsys Milkyway format, экстрагированные и rtl-нетлисты. В зависимости от условий распространения библиотеки она может содержать дополнительно GDS-файлы, OA- или CDBA-базу данных.

Front-end

правитьЯдром front-end описания является характеризованная библиотека стандартных элементов. Промышленным форматом де-факто стал Synopsys Liberty Format (.lib), хотя существуют и альтернативные форматы, например, ALF (Advanced library format).

Оригинальный .lib содержит в себе временные характеристики ячеек в табличной форме (NLDM). Обычно используются 2-мерные таблицы, описывающие задержку элемента в зависимости от нагрузки и времени входного фронта. Однако при увеличении скорости ИС точности данной модели оказалось недостаточно. Проблема NLDM-модели была в том, что она не учитывала тот факт, что входная ёмкость также зависит от различных факторов, таких, как входной фронт (Эффект Миллера), состояние ячейки и т. д. Хотя NLDM-модель и поддерживает характеризацию входной ёмкости в зависимости от состояния других входов, полностью удовлетворить разработчиков она уже не могла. В ответ на это было разработано 2 расширения для .lib-формата:

- Компания Synopsys предложила CCS- (Composite Current Source) модель. Данная модель учитывала изменение входной ёмкости в зависимости от других факторов[3]

- В ответ на CCS организация EDA разработчиков Si2.org совместно с Cadence предложили open-source ECSM- (Effective Current Source Model) модель, которая также использовала нелинейную модель входного фронта, что позволяло более точно вычислять входную ёмкость[4]

.lib-библиотеки содержат не только информацию о задержках, но и о потребляемой мощности (как динамической, так и статической и внутренней), её площади, функциональности, шумах и т. д.

Обычно библиотека содержит несколько .lib-файлов: элементы обсчитывают на наилучший (максимальная скорость: максимальное напряжение, минимальная температура), наихудший (минимальная скорость: минимальное напряжение и максимальная температура) и типичный случай (номинальные скорость, напряжение и температура). Так же могут использовать специальные PVT (Process, voltage, temperature), например, для характеризации электромиграции используется pvt с максимальными напряжением и температурой, чтобы обеспечить максимальный ток.

Verilog- и/или VHDL-модели также является важнейшей частью библиотеки стандартных элементов. Они содержат функциональное описание ячейки, а также соответствие с .lib для правильной SDF-аннотации.

Также к front-end относят вспомогательные компоненты, например, stub-модели для формальной верификации LEC.

Back-end

правитьLEF (Layout exchange format) условно делится на библиотечную и технологическую части

- Библиотечная часть содержит геометрические сведения о внешней физической структуре ячеек. Фактически, это внешняя геометрия ячеек, блокиджей и информация о расположении входов и выходов.

Данная абстракция рекомендуется для использования при размещения и разводки элементов на кристалле, так как информация о внутренней структуре ячейки для этого не важна, а использование GDS (полного описания физической структуры ячеек) приведет к фатальному увеличению используемой памяти при размещении/разводке.

- Технологическая часть содержит разнообразные правила проектирования, необходимые для размещения и разводки чипа: требования к размерам металла, к плотности размещения, к спейсингам (расстояния между соседними блокиджами, переходами (via), металами, ячейками и т. д.), плотностям тока (требования к электромиграции) и множество другой технологической информации. Эта информация используется place/route САПР для правильного размещения и разводки в соответствии с технологическими нормами.

.lib-формат также может использоваться для этих целей.

Вторая важная деталь back-end-наполнения библиотеки стандартных элементов — это нетлисты. Нетлисты поставляются в экстрагированном виде (содержит не только активные элементы: транзисторы и диоды, но и пассивные: резисторы, ёмкости и индуктивности). Также могут поставляться неэкстрагированные нетлисты, которые, в частности, используются для LVS.

Для каждой логической функции библиотека может предоставлять множество ячеек, реализующих её, но различающихся по мощности, задержкам или другим параметрам.

Плюсы и минусы методологии стандартных ячеек

правитьМетодология стандартных ячеек позволяет разработчикам конструировать ИС не на транзисторном уровне, а на уровне абстрактных стандартных элементов, что позволяет существенно сократить время и усилия для создания схемы:

- Проектирование из готовых блоков существенно упрощает и ускоряет разработку

- Использование абстрактных представлений физической реализации ячеек позволяет существенно сократить использование памяти рабочей станции, что удешевляет (за счет меньших требований к конфигурации рабочих станций) и ускоряет процесс размещения и разводки.

- Использование таблиц с задержками и подобной информацией позволяет сократить время моделирования схемы с нескольких недель или дней до нескольких часов по сравнению с транзисторным моделированием.

Однако у этой технологии есть и ряд минусов:

- Так как набор стандартных элементов ограничен, процесс проектирования на основе этой методологии не очень гибок. В практическом плане это означает, что размер полученной ИС будет больше по сравнению с аналогичной схемой, разработанной на транзисторном уровне

- За счет аппроксимации временных параметров, занесенных в таблицы библиотеки, результаты моделирования ИС получаются приблизительными и могут быть использованы лишь на стадии проектирования схемы.

- Проект сильно зависит от качества библиотеки

Несмотря на эти минусы, методология стандартных ячеек стала стандартом де-факто в сфере микроэлектроники.

Мера сложности

правитьДля разработок на базе стандартных ячеек обычно используется независимая от технологии производства метрика (транзисторный эквивалент).

См. также

правитьПримечания

править- ↑ Cerebras Wafer Scale Engine — гигантская микросхема размером с iPad Pro, с более чем 1 трлн транзисторов и TDP в... 15 кВт Архивная копия от 7 октября 2019 на Wayback Machine, 20 августа 2019 - "процессор Intel NNP-T, ..27 млрд транзисторов. .. GPU Nvidia TU102,.. содержит 18,6 млрд транзисторов, а GV100 — 21,1 млрд"

- ↑ Inside Volta: The World’s Most Advanced Data Center GPU (англ.). NVIDIA Developer Blog (10 мая 2017). Дата обращения: 11 декабря 2019. Архивировано 9 января 2018 года.

- ↑ Архивированная копия. Дата обращения: 4 июня 2010. Архивировано из оригинала 24 сентября 2015 года.

- ↑ Cadence ECSM Library Format. Дата обращения: 4 июня 2010. Архивировано 11 мая 2009 года.

Ссылки

править- VLSI Technology— This site contains support material for a book that Graham Petley is writing, The Art of Standard Cell Library Design

- Asic Service — overview of Standard Cell as well as white papers.

- Oklahoma State University— This site contains support material for a complete System on Chip standard cell library that utilizes public-domain and Mentor Graphics/Synopsys/Cadence Design System tools

- Virginia Tech— This is a standard cell library developed by the Virginia Technology VLSI for Telecommunications (VTVT)

- ChipX — Interesting overview of Standard Cell as well as metal layer configurable chip options.