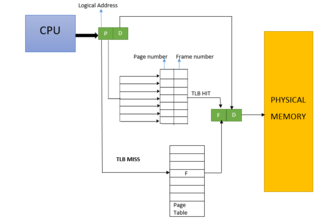

Буфер ассоциативной трансляции (англ. translation lookaside buffer, TLB) — специализированный кэш центрального процессора, используемый для ускорения трансляции адреса виртуальной памяти в адрес физической памяти.

Обзор

правитьTLB используется всеми современными процессорами с поддержкой страничной организации памяти. TLB содержит фиксированный набор записей (от 8 до 4096) и является ассоциативной памятью. Каждая запись содержит соответствие адреса страницы виртуальной памяти адресу физической памяти. Если адрес отсутствует в TLB, процессор обходит таблицы страниц и сохраняет полученный адрес в TLB, что занимает в 10—60 раз больше времени, чем получение адреса из записи, уже закэшированной TLB. Вероятность промаха TLB невысока и составляет в среднем от 0,01 % до 1 %.

Переключение задач

правитьЕсли целевая задача при переключении контекста использует отличный от предыдущего контекст памяти (каталог страниц и таблицы страницы), происходит очистка TLB, таким образом при последующих обращениях в память снижается производительность процессора (необходима подгрузка записей таблицы страниц в пустой TLB). Существует несколько стратегий борьбы с очисткой:

- сохранение TLB в оперативной памяти;

- спецификация принадлежности записи TLB к определённому адресному пространству.

Многоуровневые TLB

правитьВ современных процессорах может быть реализовано несколько уровней TLB с разной скоростью работы и размером. Самый верхний уровень TLB будет содержать небольшое количество записей, но будет работать с очень высокой скоростью, вплоть до нескольких тактов. Последующие уровни становятся медленнее, но вместе с тем и больше.

Иногда верхний уровень TLB разделяется на 2 буфера, один для страниц, содержащих исполняемый код, и другой — для обрабатываемых данных.

Характеристики

правитьТипичные характеристики для процессоров в 2009 году[1]:

- Размер: 12 бит — 4096 записей;

- Время запроса данных, хранящихся в TLB (Hit time): 0,5 — 1 такт;

- Время при «промахе» (Miss penalty): 10 — 100 тактов;

- Интенсивность промахов: 0,01 — 1 %.

TLB и большие страницы

правитьМногие современные процессоры поддерживают 2 типа страниц, обычные и большие (Huge Page). Например, процессоры x86 обычно работают со страницами размера 4 КБ, но допускают использование 4 МБ страниц при помощи PSE. Для процессоров x86-64 доступны большие страницы размером 2 МБ[2] (и 1 ГБ для некоторых моделей).

Записи трансляции для больших таблиц также хранятся в TLB, но на некоторых процессорах для них используется отдельный TLB в 4 — 8 записей.

Примечания

править- ↑ John L. Hennessy. Computer Organization And Design. Hardware/Software interface. 4th edition (англ.). — Burlington, MA 01803, USA: Morgan Kaufmann Publishers, 2009. — P. 503. — 703 p. — ISBN 978-0-12-374493-7.

- ↑ Hugepages — Debian Wiki. Дата обращения: 1 июня 2012. Архивировано 30 апреля 2012 года.

Ссылки

правитьВ другом языковом разделе есть более полная статья Translation lookaside buffer (англ.). |